Technology

RISC-V CPU IP, Chiplets and Platforms

Product

Information

Veyron V1 and V2

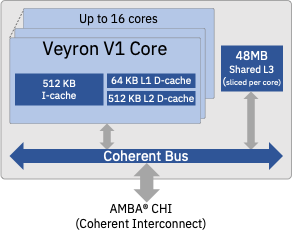

Ventana's first and second-generation RISC-V high-performance CPUs represent a significant leap in technology targeted at data center, edge, and other general computing applications. Both are designed for integration as IP within an SoC, delivered as an optimized compute chiplet, or within an ASSP/CSSP SiP standard product.

Veyron V1 and V2 are server-class CPUs, engineered to exceed the demands of virtualized cloud-native workloads and robust data center requirements. The Veyron IP portfolio includes advanced RISC-V system IP components such as an IOMMU. Its interface complies with common AMBA protocol standards, facilitating the integration of complete high-performance system solutions with available third-party IP.

CPU IP

Performance

- Enhanced fifteen-wide aggressive out-of-order pipeline

- Advanced cache hierarchy with large high-bandwidth cluster-level shared L3 cache (up to 128MB)

- Enhanced BTB/TLB structures crucial for data center applications

- RVV1.0 512b vector unit and Ventana AI matrix extensions

Perf/W Optimization

- Configurable TDP for the desired performance-power profile

- Turbo profile management to maximize performance within a TDP

- Cluster-level and per-core digital power models to control turbo behavior

Server-Class

- Full architectural support for virtualized workloads

- Comprehensive RAS (ECC, error logging/scrubbing, data poisoning)

- Advanced side-channel attack mitigations

- Top-down performance analysis methodology for software optimization

Implementation Details

- Configurable as multi-core clusters supporting high core count scalability

- Highly portable design with no custom macros or RAM dependencies

Chiplets

Rapid Deployment

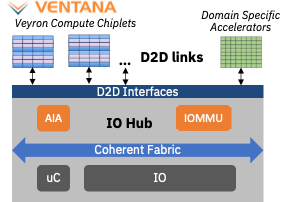

- Chiplets logically interface as an AMBA CHI RN-F CPU cluster

- D2D link optimized for ultra-low latency, crucial to CPU performance

- Adherence to UCIe chiplet interfacing standard

CPX System IP

Ventana provides the Veyron V1 and V2 CPX (Cluster Proxy) IP for the companion IO Hub SoC integration to seamlessly interface with Veyron compute chiplets.

Product (System in Package)

Contact us to explore the following ASSP solutions with Veyron technology:

- Accelerated DPUs

- Accelerated 5G Open RAN platforms

- High-performance servers and edge compute platforms

Have a specific need? Contact us to see how Ventana’s vast partner ecosystem and the Veyron V1 or V2 can assemble a CSSP to meet your needs.

Careers